- 您现在的位置:买卖IC网 > Sheet目录2008 > MAX1202AEPP+ (Maxim Integrated Products)IC ADC 12BIT 8CH 20-DIP

MAX1202/MAX1203

5V, 8-Channel, Serial, 12-Bit ADCs

with 3V Digital Interface

18

______________________________________________________________________________________

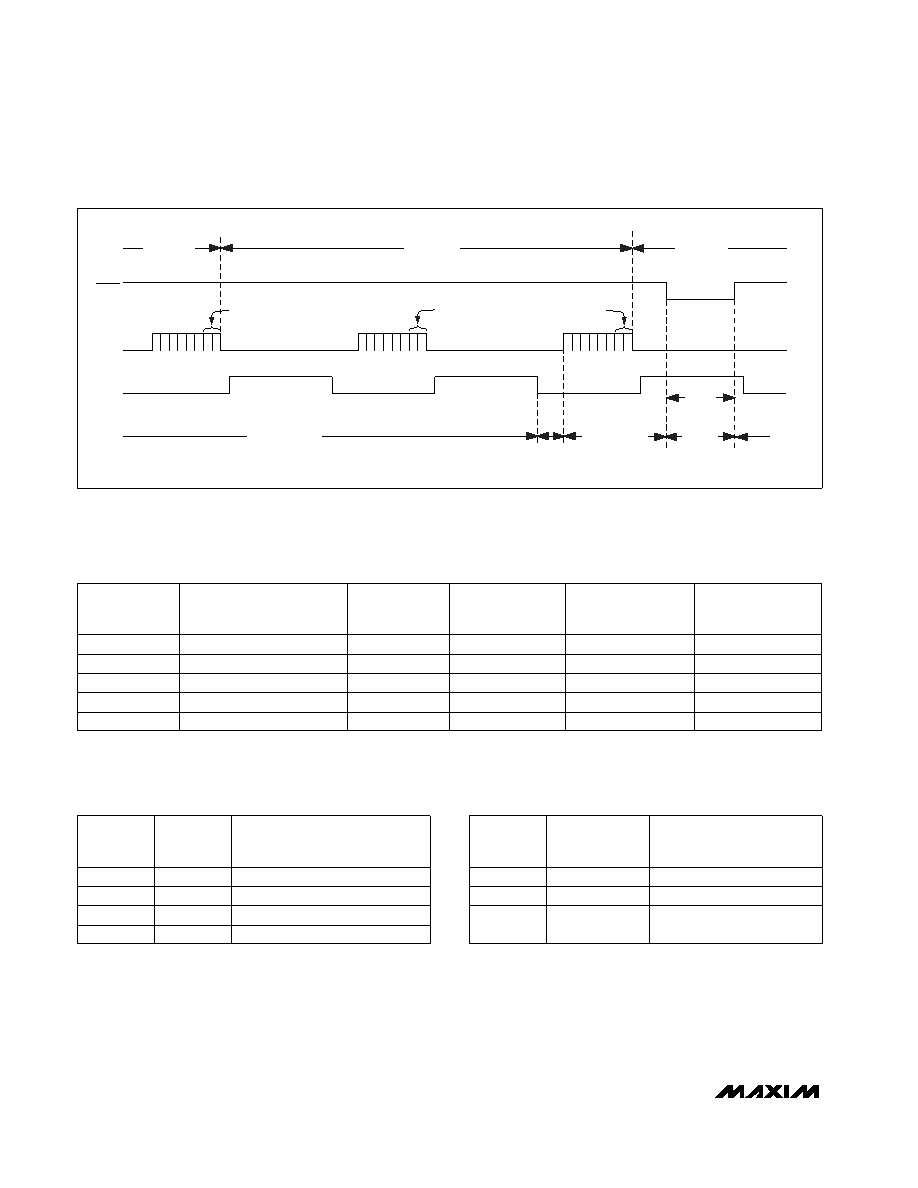

Table 6. Software Shutdown

and Clock Mode

Table 5. Typical Power-Up Delay Times

Table 7. Hard-Wired Shutdown

and Compensation Mode

Figure 12a. Timing Diagram for Power-Down Modes, External Clock

POWERED UP

FULL

POWER-

DOWN

POWERED

UP

POWERED UP

DATA VALID

(12 DATA BITS)

DATA VALID

(12 DATA BITS)

DATA

INVALID

EXTERNAL

INTERNAL

SX XXXX 11

S

0 1

XX

X

X X XXX

S1 1

FAST

POWER-DOWN

MODE

DOUT

DIN

CLOCK

MODE

SHDN

SETS EXTERNAL

CLOCK MODE

SETS EXTERNAL

CLOCK MODE

SETS FAST

POWER-DOWN

MODE

133

2

Full

Disabled

133

2

Fast

Disabled

133

26

MAXIMUM

SAMPLING RATE

(ksps)

See Figure 14c

300

5

POWER-UP

DELAY

(s)

Fast/Full

Full

Fast

POWER-DOWN

MODE

4.7

REF

CAPACITOR

(F)

External

Enabled

REFERENCE

BUFFER

Internal

Enabled

Internal

Enabled

REFERENCE-BUFFER

COMPENSATION MODE

N/A

Full

Power-Down

GND

S

SH

HD

DN

N

STATE

External compensation

Enabled

Floating

Internal compensation

Enabled

VDD

REFERENCE-BUFFER

COMPENSATION

DEVICE

MODE

External clock mode

1

Internal clock mode

0

1

PD1

Fast power-down mode

1

0

Full power-down mode

0

DEVICE MODE

PD0

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX121EAP+

IC ADC 14BIT 308KSPS 20SSOP

MAX1238MEEE+T

IC ADC 12BIT SERIAL 16-QSOP

MAX1240AEPA+

IC ADC 12BIT SERIAL 8-DIP

MAX1245BCPP

IC ADC SRL 12BIT 2.375V 20-DIP

MAX1249AEPE+

IC ADC 10BIT SERIAL 16-DIP

MAX1279AETC+

IC ADC 12BIT 1.5MSPS 12-TQFN

MAX1285BESA+T

IC ADC 12BIT 300KSPS 8-SOIC

MAX1302BEUG+

IC ADC 16BIT SRL 115KSPS 24TSSOP

相关代理商/技术参数

MAX1202BC/D

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1202BCAP

功能描述:模数转换器 - ADC Integrated Circuits (ICs) RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1202BCAP+

功能描述:模数转换器 - ADC 12-Bit 8Ch 133ksps 5V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1202BCAP+T

功能描述:模数转换器 - ADC 12-Bit 8Ch 133ksps 5V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1202BCAP-T

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1202BCPP

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1202BCPP+

功能描述:模数转换器 - ADC 12-Bit 8Ch 133ksps 5V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1202BEAP

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32